The problem to solve is this: when designing a linear amplifier for a particular output-referred third-order intercept point (OIP3), what is the optimum output stage periphery and scaling factor that will achieve the target OIP3 with minimum DC power consumption?

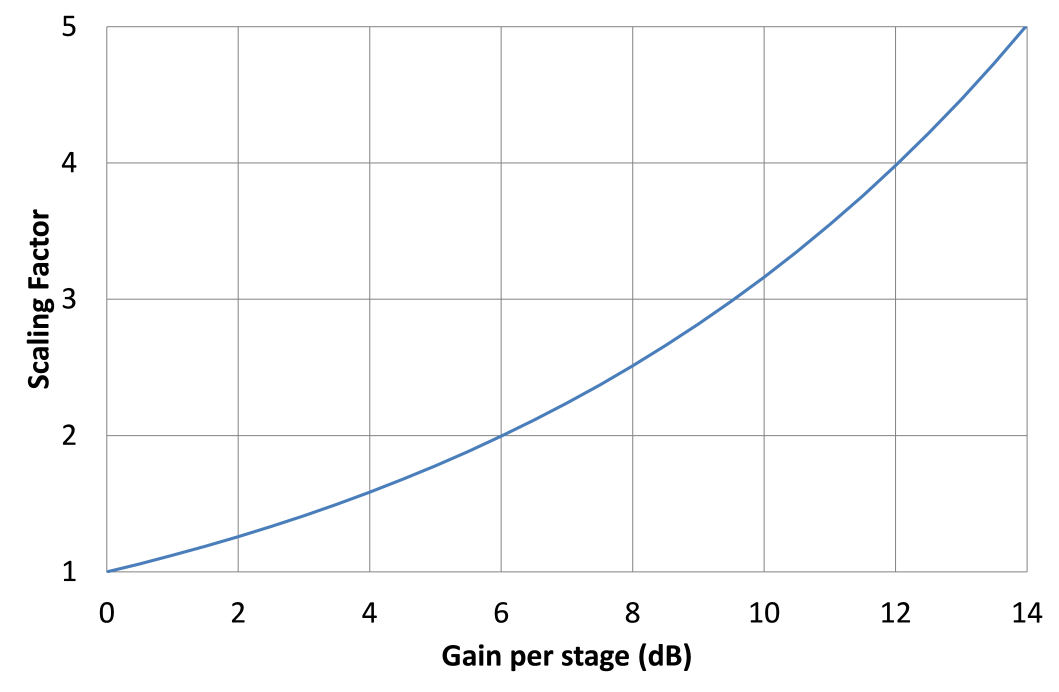

Consider an infinite cascade of amplifier stages with equal gain per stage, g. The gate width of each transistor is scaled from the preceding stage by a uniform scaling factor, s. All stages are biased class A with the same drain voltage and the same current density such that the drain currents are also scaled by s.

Let’s assume the for each transistor is 10 dB above

, where

It is usual to assume that intermodulation adds constructively in an amplifier cascade such that

In our amplifier cascade the individual stage intercept points are related according to the gate width (drain current) scaling factor:

And we assume that all stages, regardless of gate periphery, have the same small-signal gain:

The cascaded OIP3 can then be restated as

For an infinite cascade this is a geometric series which converges provided (i.e. provided the gain per stage exceeds the scaling factor). The OIP3 of the infinite cascade can therefore be simplified to

The total DC power consumption is given by another series

For an infinite cascade the total DC power consumption is

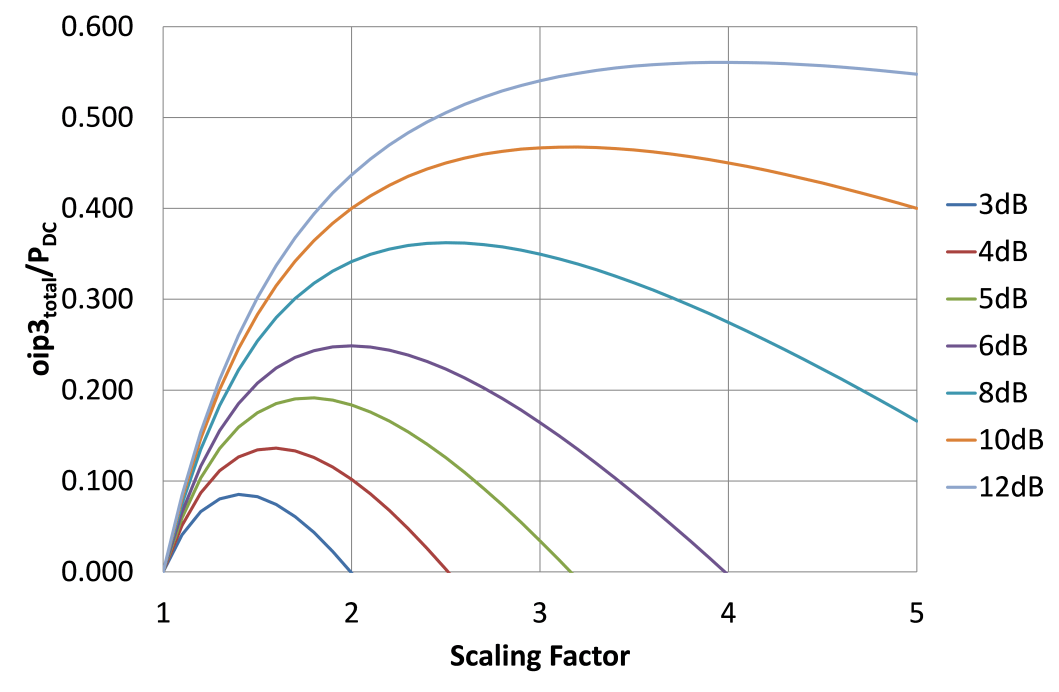

We want to maximise the ratio of to

Take the derivative with respect to scaling factor, s

The ratio of to

is maximised when

So to maximise the overall efficiency we find

and the final stage must be sized to achieve the required OIP3:

In practice, these calculations provide lower bounds on scaling factor and FET periphery. The final stage may be optimised for linearity alone. However, the matching of preceding stages is usually compromised to achieve gain flatness, bandwidth etc. They will therefore require additional margin.